网站建设需要做的事情/竞价托管公司排名

Xilinx DSP48E2 slice 在一个时钟周期内处理 INT8(8 位整数)运算的能力。

核心能力概述

一个 DSP48E2 slice 包含几个关键计算单元:

- 预加器 (Pre-Adder): 可以执行 A + D 或 A - D 操作,其中 A 是 30 位,D 是 27 位。

- 乘法器 (Multiplier): 执行 27 位 × 18 位的乘法。

- ALU (Arithmetic Logic Unit) / 后加器: 一个 48 位的单元,可以执行加法、减法、逻辑运算,并能累加乘法器的结果 § 或来自 C 输入端口的数据。

INT8 运算的并行度 (SIMD 能力)

DSP48E2 的设计允许它通过 SIMD(单指令多数据)方式,在其宽数据通路上并行处理多个较小位宽的操作,如 INT8。

-

INT8 乘法:

- 乘法器是 27x18 位。我们可以将 8 位数据(通常带符号,需要 9 位表示,即

sint<9>) 映射到这些输入。 - 27 位输入 (A) 可以容纳 三个 9 位操作数 (3 * 9 = 27)。

- 18 位输入 (B) 可以容纳 两个 9 位操作数 (2 * 9 = 18)。

- 通过特定的

OPMODE配置,DSP48E2 可以同时执行 两组 独立的 9x9(或 8x8)乘法。例如,计算A[8:0] * B[8:0]和A[17:9] * B[17:9]。 - 结论: 一个 DSP48E2 在一个时钟周期内最多可以执行 2 次 INT8 乘法。

- 乘法器是 27x18 位。我们可以将 8 位数据(通常带符号,需要 9 位表示,即

-

INT8 加法/减法:

- 预加器 (A+D): A 输入 30 位,D 输入 27 位。理论上,30 位可以容纳 3 个 8/9/10 位操作数,27 位也可以容纳 3 个 8/9 位操作数。通过 SIMD 配置,预加器可能支持最多 3 次 并行的 INT8 加/减法。

- ALU/后加器 (48 位): 这个单元功能更强大,有 48 位宽。

- 它可以被配置为执行多个并行的较小位宽算术/逻辑运算。

- 48 位可以容纳 六个 8 位操作数 (6 * 8 = 48)。

- 通过合适的

ALUMODE和OPMODE设置,ALU 理论上可以支持最多 6 次 并行的 INT8 加法、减法或逻辑操作。

- 结论:

- 使用预加器,最多 3 次 INT8 加/减法。

- 使用 ALU/后加器,最多 6 次 INT8 加/减法/逻辑运算。

- 注意: 能否同时利用预加器和后加器进行 独立的 INT8 加法,取决于具体的流水线和操作模式配置。通常,它们是串联路径的一部分(例如,预加结果送入乘法器,乘法器结果送入后加器)。但在某些模式下,它们可能被用于不同的并行计算。

总结

在一个时钟周期内,一个 Xilinx DSP48E2 slice 的 INT8 运算能力上限是:

- 乘法: 最多 2 次 INT8 乘法。

- 加法/减法:

- 理论上,ALU 最多可执行 6 次 INT8 加/减法/逻辑运算。

- 预加器最多可执行 3 次 INT8 加/减法。

实际应用中的考虑:

- Multiply-Accumulate (MAC): 最常见的 DSP 应用是 MAC。DSP48E2 可以执行 2 次 INT8 乘法,并将这两个 16 位(或更高位宽,考虑累加)的结果在同一个周期内送入 48 位 ALU 进行累加。这通常被计为 2 个 INT8 MAC 操作 / 周期。

- 工具推断: HLS 或 RTL 综合工具能否自动推断出这些复杂的 SIMD 模式,取决于代码的写法和使用的 pragma/属性。要达到理论最大值,有时需要手动实例化 DSP 宏或者使用特定的编码风格。

- 配置: 实现这些并行度的前提是正确配置 DSP slice 的

OPMODE,ALUMODE等控制信号。

因此,当评估性能时,通常认为 DSP48E2 提供 2 个 INT8 乘法 的能力,并配合强大的 并行加法/累加 能力。

计算理论最大INT8性能

文献结果

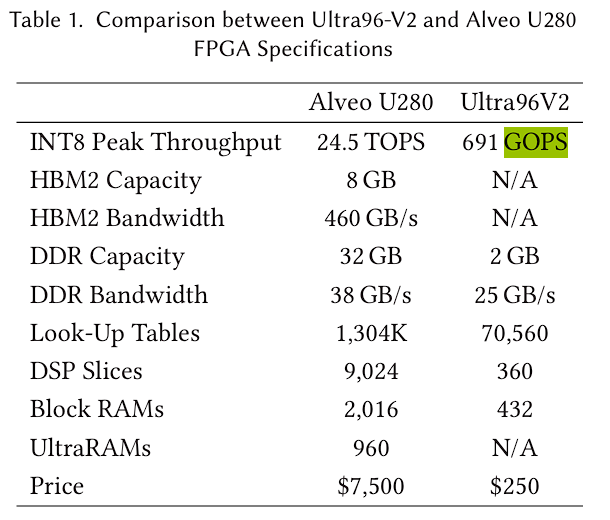

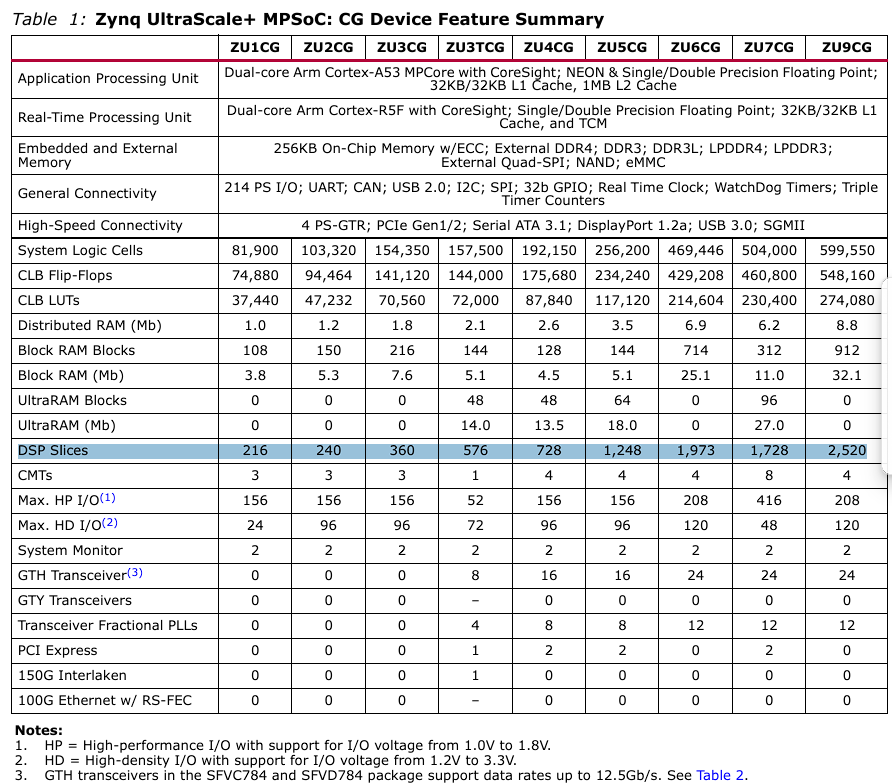

我们用Ulitra96V2这款常见的入门板子计算,他是ZU3CG芯片

来源 FPGA-based Acceleration of Time Series Similarity Prediction: From Cloud to Edge

他有360个DSP单元可配置,

如果不考虑数据从哪来,理论最大是 (2次乘法+4次加法) X 360(器件数量) X 300 M(时钟频率) = 648 Gops

虽然我们也不知道文献里面的691GOPS怎么算的,但差的不多